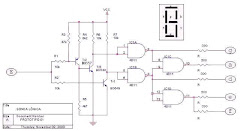

En la sonda que se presenta en la figura 2, trata de un circuito más elaborado y cercano a los nivelas CMOS, aunque los niveles que presenta para TTL, no son del todo rigurosos, se pueden aceptar como buenos.

En dicho esquema, se aprecia una fuente de corriente constante de unos 15mA, formada por los componentes pasivos: Tr1, R3, R4, D5 y D6, la cual se encarga de alimentar el LED correspondiente, según el nivel lógico detectado.

Los diodos D1 y D2, sirven de protección para la sonda, contra tensiones fortuitas de hasta 100V. Si a la conexión "terminal libre" de R1 de 100k, se aplica una tensión elevada respecto a masa, la puerta inversora N1 del circuito integrado CMOS, invertirá este nivel y el cátodo de D3 (Rojo) se pondrá a masa, por consiguiente se iluminará, indicando un nivel lógico alto H.

Mientras tanto el nivel del cátodo de D4 (Verde), permanecerá alto gracias a la nueva inversión producida por N2, y por consiguiente, dicho diodo no se iluminará. Sólo se iluminará cuando al extremo libre de R1 se le aplique una pequeña tensión, respecto a masa inferior a 1/3 de la tensión de alimentación, en cuyo caso el nivel bajo 0, se transmitirá hasta el cátodo de D4 y éste se iluminará indicando un nivel lógico L, lo que conlleva que el diodo D3 se desactive permaneciendo ambos diodos en ese estado hasta que se produzca un cambio en la entrada.

La resistencia R2 tiene encomendadas las funciones de limitar la carga que presentará la sonda al circuito bajo prueba por una parte y pone a masa al primer inversor N1 cuando no se aplica tensión alguna a la entrada, evitando así que las puertas N1 y N2 entren en auto-oscilación por la gran sensibilidad que estas presentan por tratarse de CMOS.

Suscribirse a:

Enviar comentarios (Atom)

No hay comentarios:

Publicar un comentario